X800 Architecture Overview

As mentioned above, the Radeon X800 XT is a 16 pipeline configuration that also includes six vertex units, identical to the GeForce 6800 GT PCIe board SimHQ reviewed earlier this year. The following is a list of the features the X800 boards support:

Smartshader HD

- Support for DirectX 9.0 programmable vertex and pixel shaders in hardware

- DirectX 9.0 Vertex Shaders

- Vertex programs up to 65,280 instructions with flow control

- Single cycle trigonometric operations (SIN & COS)

- DirectX 9.0 Extended Pixel Shaders

- Up to 1,536 instructions and 16 textures per rendering pass

- 2nd generation F-buffer technology accelerates multi-pass pixel shader programs with unlimited instructions

- 32 temporary and constant registers

- Facing register for two-sided lighting

- 128-bit, 64-bit & 32-bit per pixel floating point color formats

- Multiple Render Target (MRT) support

- Complete feature set also supported in OpenGL via extensions

Smoothvision HD

- 2x / 4x / 6x Anti-Aliasing modes

- Sparse multi-sample algorithm with gamma correction, programmable sample patterns, and centroid sampling

- Lossless Color Compression (up to 6:1) at all resolutions

- Temporal Anti-Aliasing

- 2x/4x/8x/16x Anisotropic Filtering modes

- Up to 128-tap texture filtering

- Adaptive algorithm

3Dc

- High quality 4:1 Normal Map Compression

- Works with any two-channel data format

Hyper Z HD

- 3-level Hierarchical Z-Buffer with Early Z Test

- Lossless Z-Buffer Compression (up to 48:1)

- Fast Z-Buffer Clear

- Z Cache optimized for real-time shadow rendering

Videoshader HD

- FULLSTREAM technology for Real, DivX, and WMV9 formats

- All-format DTV/HDTV decoding

- Adaptive Per-Pixel De-Interlacing and Frame Rate Conversion (temporal filtering)

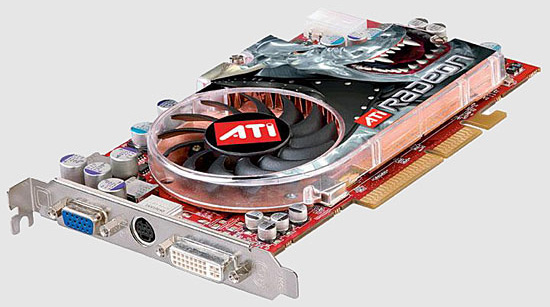

Display Features

- Dual integrated 10 bit per channel 400 MHz DACs

- Integrated 165 MHz TMDS transmitter (DVI 1.0 / HDMI compliant and HDCP ready)

- Integrated TV Output support up to 1024×768 resolution

- YPrPb component output for direct drive of HDTV displays

While the pixel shader architecture of the R420 is nearly identical to that of the R300, the newer chip has been modified to make improvements in its rendering capabilities. The number of registers and instruction limits have both been increased, which should help performance and prevent developers from running into issues with instruction lengths while developing current and near-future engines. The X800s are, however, are still Shader Model 2.0 parts and, as such, do not support features like dynamic branching and flow control, though it’s worth noting that such features are used to aid performance and not create visual effects otherwise impossible to render without SM 3.0 support. And as with the R300 architecture, the X800s use 24-bit floating point precision throughout their rendering pipelines.